The Rigel Project

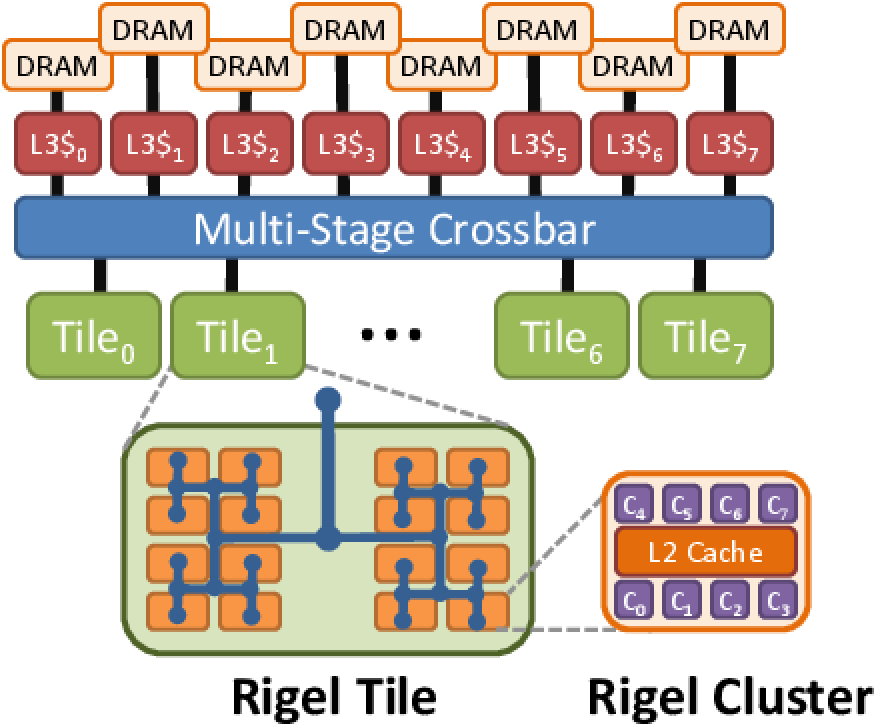

Rigel is an architecture for compute accelerators with hundreds to thousands of cores. The high-level goal of Rigel is to combine the programmability of general-purpose processors with the performance and efficiency of graphics processing units (GPUs) and other existing accelerators.

The goal of this project is to form an open, integrated ecosystem of tools for in-depth exploration of parallel architectures and parallel software.

The Rigel toolset currently includes an execution driven simulator written in C++, C99/assembly cross-compiler toolchain, system libraries, a parallel task queue library, and parallel benchmarks.

Use the Quick Start Guide to install our tools and be running 1000-core simulations within the hour.

See the University of Illinois project page for academic publications describing Rigel.

Get Involved

Our code is hosted on github.

We are actively seeking contributions for all parts of the toolset.

We intend to cultivate a vibrant community around these tools, and will work with you to upstream your enhancements.

We have many existing project ideas for people with a wide range of expertise and interests. We will post a list of ideas in the near future.

Our contributor policy and coding standards are a work-in-progress; post to the mailing list with suggestions.

Send us a pull request, file a bug, or see the Contact page to get involved!